데이터 용량 15배…인공지능 PIM반도체 세계 첫 개발

카이스트 연구팀

국내 연구진이 기존보다 15배 더 많은 데이터를 처리할 수 있는 인공지능용 PIM 반도체를 개발했다.

카이스트(KAIST) 연구진이 국내 최초로 DRAM 메모리 셀 내부에 직접 연산기를 집적해 기존보다 15배 더 많은 용량의 인공지능(AI) 연산을 수행할 수 있는 PIM 반도체인 ‘다이나플라지아(DynaPlasia)’를 개발했다고 14일 밝혔다.

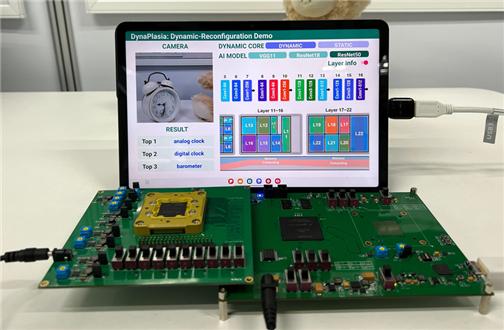

다이나플라시마 DynaPlasia 데모 실시간 물체 인식 시스템에서 DynaPlasia 칩에 다양한 인공지능 모델 구조에 맞춰 성능을 최적화 할 수 있다. 각각의 인공지능 모델 (심층신경망)은 여러 레이어로 구성 되어있는데, 모델 구조가 변경 되면 각 레이어에 맞게 하드웨어 구조가 변경된다. 또한 하드웨어 구조 변경에 따라 메모리와 연산기간에 리소스가 동적으로 전환 되는 것을 확인할 수 있다. 그림제공=카이스트

다이나플라이자는 Dyna(동적으로, DRAM 기반으로)와 Plasia(목적에 맞춰 구조를 형성)의 합성어다. DRAM 기반으로 필요에 맞춰 하드웨어 구조를 형성해 다양한 인공지능 모델을 처리 가능하다는 의미다.

PIM(Processing-In-Memory)이란 하나의 칩 내부에 메모리와 프로세서 연산기를 집적한 차세대 반도체다. 메모리와 프로세서가 분리되어 있는 기존 컴퓨팅 구조(폰 노이만 구조)에서 발생하는 데이터 병목현상 및 과다한 전력 소모 문제를 해결할 수 있다.

기존에도 PIM 반도체가 개발되기는 했지만, 대부분 셀 하나에 8개 이상의 트랜지스터가 필요한 SRAM-PIM 방식이거나, 기존 PIM(HBM-PIM, GDDR6-AiM 등)과 같이 DRAM 기반 PIM으로 구현되었더라도 연산기를 메모리 셀 어레이의 내부가 아닌 외부에 근접하게 배치하는 디지털 PIM(Near Memory PIM) 방식이었다. 이러한 디지털 PIM 방식은 메모리와 연산기 사이의 거리를 줄이고 대역폭을 넓혀 데이터 병목현상은 감소하였지만 메모리 셀 내부에 직접 연산기를 집적하여 연산성능을 올리지는 못했다.

연구팀이 개발한 다이나플라지아(DynaPlasia)는 아날로그형 DRAM-PIM 기반 AI 반도체다. 3개의 트랜지스터만으로 셀을 구성했다. 메모리 셀 내부에 연산기를 집적하고 높은 병렬성과 에너지 효율의 아날로그 연산 방식을 이용해 집적도와 연산기능을 획기적으로 향상시켰다. 누설전류 내성 컴퓨팅을 통해 모든 메모리 셀들이 병렬로 동작할 수 있도록 했다. 기존 디지털 DRAM-PIM 방식 대비 약 300배 높은 병렬성으로 15배 높은 데이터 처리량을 보인다. 메모리 셀 내부의 값이 누설전류에 의해 점차 소실되는 DRAM의 특성상, 기존에는 높은 병렬성의 아날로그형 DRAM-PIM의 구현이 어려웠다. 연구팀은 셀 내부 곱셈 로직에서 누설전류의 영향을 없앤 후 아날로그 연산을 수행해 모든 메모리 셀들이 병렬로 동작 가능하도록 했다.

또 기존 아날로그형 PIM 반도체에서는 메모리와 연산기, 그리고 아날로그-디지털 데이터 변환기를 별도로 구현하여 고정된 하드웨어 구조를 사용했지만 연구팀은 세계 최초로 하나의 셀이 메모리, 연산기, 데이터 변환기의 기능을 동시에 지원할 수 있는 ‘트리플-모드 셀’을 개발했다. 이에 따라 실제 인공지능 연산에 맞춰 하드웨어 구조를 형성하는 동적 코어 형성 아키텍처로 기존 아날로그형 PIM 반도체보다 2.5배 가량 높은 효율성을 얻는다.

이번 연구 결과는 지난달 미국 샌프란시스코에서 개최된 국제고체회로설계학회(ISSCC)에서 발표됐다.

꼭 봐야 할 주요 뉴스

"국민들 대다수는 원하지 않았는데"…기름값으로 6...

"국민들 대다수는 원하지 않았는데"…기름값으로 6...

유회준 카이스트 전기전자공학부 교수는 “이번 연구는 기존 인공지능 반도체가 가지고 있던 메모리 병목현상을 해소할 뿐만 아니라, 높은 처리량과 가변성을 갖는 고메모리 용량의 DRAM-PIM을 개발했다는 점에서 의미가 크다"면서 "본격적인 상용화에 성공할 경우, 최근 더욱 거대해지고 다양해지는 인공지능 모델에서도 높은 성능을 보일 수 있을 것”이라고 말했다.

<ⓒ투자가를 위한 경제콘텐츠 플랫폼, 아시아경제(www.asiae.co.kr) 무단전재 배포금지>

!['마이쭈'보다 싼 주사제…소아 필수약인데 만들수록 손해[Why&Next]](https://cwcontent.asiae.co.kr/asiaresize/308/2026051811210766990_1779070866.png)

![[단독]예산보호막 사라진 디지털배움터, 재정열악 지자체선 축소·소멸될 수도](https://cwcontent.asiae.co.kr/asiaresize/308/2026051808275866381_1779060477.png)

![[초동시각]증시활황이 불러온 긍정 효과들](https://cwcontent.asiae.co.kr/asiaresize/308/2026051811030357256A.jpg)

![[에너지토피아]전기 버리는 유럽, 남의 일 아니다](https://cwcontent.asiae.co.kr/asiaresize/308/2026051815313149170A.jpg)

![[트레이드 오프]안보보다 경제가 급했다](https://cwcontent.asiae.co.kr/asiaresize/308/2026051811180517690A.jpg)

![2주만 참으면 항공권 '핫딜' 뜬다…해외여행 들썩[비주얼뉴스]](https://cwcontent.asiae.co.kr/asiaresize/308/2026051815013167296_1779084091.jpg)

![[르포]"전가구 100% 남향·한강조망"…DL이앤씨, 압구정5구역 조합원 표심잡기](https://cwcontent.asiae.co.kr/asiaresize/308/2026051812040467045_1779073444.jpg)

![[속보]법원, 삼성전자 노조에 제동…파업 범위 위반 시 ‘하루 1억’ 배상](https://cwcontent.asiae.co.kr/asiaresize/309/2026051719315966137_1779013920.png)

![유통책이 물었다…유흥가, 얼마나 알고 있나[취藥국가]①](https://cwcontent.asiae.co.kr/asiaresize/309/2026051318172661825_1778663847.png)

![[취藥국가]⑤"감옥에서 김치까지"…캄보디아 총책 '송'](https://cwcontent.asiae.co.kr/asiaresize/309/2026012809163418359_1769559394.jpg)