"Blocked Current Leakage with Sandwich Structure"... DGIST Develops Next-Generation 3D Semiconductor Transistor [Reading Science]

Stable Operation Achieved in Two-Dimensional Nano-Channels with "Dual-Modulated Vertically Stacked Transistor"

Scalable to Large-Area and Multilayer Fabrication Without Costly Ultra-Precise Processes

Published in the International Journal Ad

A new design strategy has been proposed to overcome the structural limitations of three-dimensional (3D) stacked transistors, a key technology for next-generation highly integrated semiconductors. The development of a transistor structure that operates stably and suppresses current leakage even at the nanometer scale ultra-fine channels has opened up new possibilities for low-power, high-density semiconductor design in the future.

The research team led by Professor Jae Eun Jang from the Department of Electrical Engineering, Electronics, and Computer Science at Daegu Gyeongbuk Institute of Science and Technology (DGIST) announced on March 12, 2026, that they have developed, for the first time in the world, a 'dual-modulated vertically stacked transistor' that operates stably even with a two-dimensional nano-channel structure. The research results were published in the international journal Advanced Science.

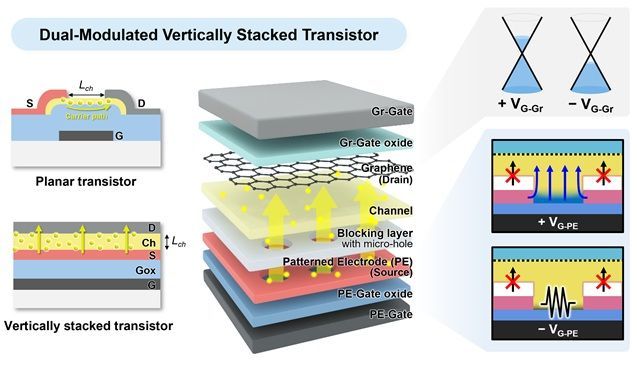

Structural difference between a conventional transistor and a planar stacked transistor (left), and a conceptual diagram showing the layer structure and operating principle of a dual-modulation planar stacked transistor. Provided by the research team

View original imageRecently, as the demand to integrate more devices into a limited area has increased, the semiconductor industry has been facing the physical limits of miniaturization. As an alternative to overcome these limits, the planar stacked transistor structure—which vertically stacks channels through which current flows—has been gaining attention as a next-generation 3D semiconductor technology.

However, in existing structures, the electrodes shield the electrical signal, preventing the gate signal from being evenly delivered across the entire channel. The so-called 'short-channel effect,' where current leaks or device operation becomes unstable as the channel length shortens, was a major limitation.

To address this, the research team proposed a 'dual-modulation structure,' in which upper and lower gates control the channel in different ways, with the gates positioned on either side of the channel. This sandwich-like design uses top and bottom electrodes to control the current flow through the channel.

Specifically, micro-holes were formed in the lower electrode so that the electric field can penetrate deeper into the channel, while the upper electrode was made of graphene, a new material, to precisely regulate current flow. In addition, a blocking layer was added to regions prone to current leakage to prevent unnecessary power loss.

As a result, the research team succeeded in suppressing leakage current to the 10⁻¹²A (ampere) level when the power is off, even in ultra-thin channels at the nanometer scale. At the same time, they achieved high switching performance for clearly distinguishing between the on and off states of the power supply, and ensured sufficient output current even at low voltages. The transistor also showed stable operation under external stress conditions, such as exposure to light or extended operation times.

This technology does not require expensive ultra-precise alignment or high-temperature processes, making it easy to scale up to large-area processes and multi-layer stacked structures. The research team expects that, in addition to highly integrated 3D semiconductors, the technology can be applied in various fields, including low-power logic devices, next-generation memory, and flexible electronic devices.

Professor Jang said, "We proposed a new dual-gate design strategy that enables stable operation even in nano-scale channels," adding, "It is a structure that can overcome the fundamental limitations of conventional vertical transistors and will be an important solution for the development of next-generation low-power, highly integrated 3D semiconductor technology."

Hot Picks Today

!["Stock Set to Double: This Company Smiles Every Time a Data Center Is Built [Click e-Stock]"](https://cwcontent.asiae.co.kr/asiaresize/93/2026050416112750184_1777878687.jpg) "Stock Set to Double: This Company Smiles Every...

"Stock Set to Double: This Company Smiles Every...

- "Is Yours Just Gathering Dust at Home? Millennials & Gen Z Rediscover Digicams O...

- "Continuous Groundwater Pumping Causes Mexico City to Sink 24cm Annually... 'Gia...

- "I Take Full Responsibility"... Seongjae Ahn Issues Direct Apology for 'Wine Swi...

- “She Shouted, ‘The Rope Isn’t Tied!’... Chinese Woman Falls from 168m Cliff ...

This research was supported by the InnoCORE project of the Ministry of Science and ICT and the National Research Foundation of Korea.

© The Asia Business Daily(www.asiae.co.kr). All rights reserved.